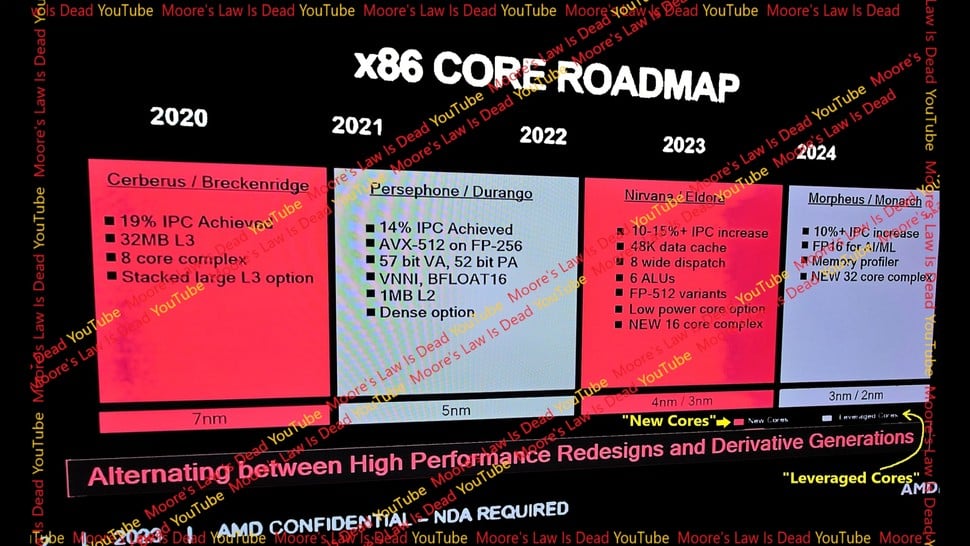

Moore’s Law Is Dead, which publishes leaks with information obtained from various sources, shared some images that allegedly belong to official AMD slides. The leak focuses on the red team’s Zen 5 and Zen 6 architectures. Let’s look at the details together.

AMD Zen 5 Architecture

It’s worth noting that these slides are strictly aimed at AMD’s enterprise server chips (EYPC) and not focused on mainstream consumer desktop CPUs. So don’t expect every new feature, such as FP-512 support, to be included in Ryzen 8000 processors. However, basic architectural developments also concern us, the end consumers.

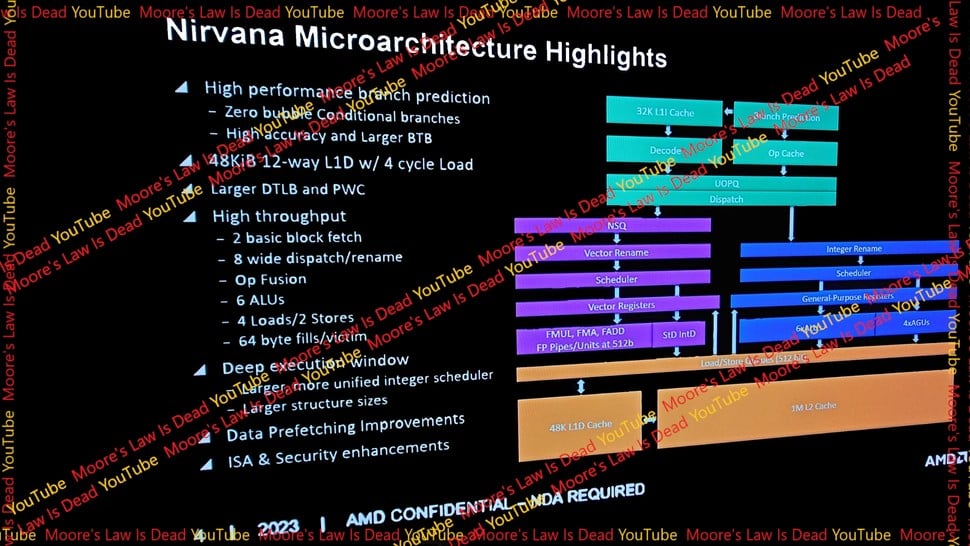

Apparently, Zen 5 architecture chips, codenamed Nirvana, will be developed with new 4nm/3nm manufacturing processes. Zen 5 architecture will be a significant revision compared to the current Zen 4 architecture, and will come with around 10-15% IPC gain. It is also stated that IPC improvement can be made at higher levels. However, it is reported that Zen 5 will use 16-core CCXs (units-complexes where the cores are located) for the first time.

The list of improvements to the Zen 5 core is quite extensive. The biggest gains are on the L1 cache, branch predictor, execution window, and core processing efficiency side. While Zen 5’s L1 cache size was 32 KB in Zen 4, it increases to 48 KB in Zen 5.

The chip’s throughput has reportedly been extensively improved to include 2 basic block fetch units, 8 wide send/rename units, 6 ALUs, 4 load and 2 store units, and more. It is stated that the timer now has a larger structure size and the integer timer is larger and more unified than previous designs. The slide also lists ISA and Security enhancements, as well as improvements to “prioritized data fetching” processes, but no details are provided.

CCXs in AMD processors have until now been able to accommodate a maximum of 8 cores. Nothing has changed since the Zen 2 architecture. If we talk about the most important development, the core configuration in Zen 5 CCXs has been increased from 8 to 16.

So the number of CCXs may increase for the first time since Zen 2. Well what does it mean? The flagship processor, potentially called Ryzen 9 8950X, could come with 32 cores and 64 threads. We’re not saying this will happen for sure, but if the leaks are true, AMD can produce such a CPU if it wants.

We don’t yet know what kind of cores the Zen 5 core clusters will have. As you know, the company started to use small cores called “Zen 5c” in its EPYC processors, focusing on efficiency. Perhaps we can see the same approach in consumer-grade desktop CPUs. Half of the cores may consist of Zen 5 and half may consist of Zen 5c cores. On the other hand, as until now, all units can be supported with Zen 5 performance cores. It could also be a mix of both, as AMD’s slides indicate there will be different models with FP-512 support and some models with lower-power cores.

Zen 5 architecture will replace the current Zen 4. We expect Ryzen 8000 desktop and mobile processors based on this architecture to be released in 2024.

AMD Zen 6 Architecture

The leaked slides also include additional predictions about AMD’s Zen 6 architecture. His codename is listed as Morpheus. The red team is expected to use 3nm and 2nm process technology here.

In the slide, it is estimated that the Zen 6 architecture will bring at least 10% IPC gain compared to Zen 5, will receive FP16 support for artificial intelligence / machine learning, and will have a new memory profiler. AMD will use the FP16 instruction set to accelerate AI/ML algorithms.

There is another important detail. We just talked about the 16-core CPU sections. It says that with Zen 6 a single unit can contain 32 cores instead of 16. We predict that not all of these will consist of Zen 6 performance cores, but there will also be Zen 6c efficiency cores.

If the leaks are true, revolutionary things will happen with Zen 6. First and foremost are the core numbers. The fact that AMD can quadruple its core count in less than three generations is impressive.

Allegedly, advanced packaging techniques underlie the Zen 6 microarchitecture. There is even talk of a chip design layout similar to Zen 2, but of course we will see major differences with interconnect techniques. In this context, it is said that AMD may integrate CCDs on the IOD (input/output interface die). If such a scenario were to occur, two important CPU units would be stacked on top of each other. Zen 6 architecture chips are expected in the second half of 2025.

Follow our site to read more technology news!